新闻资讯中心News Center

400-014-4913

钳位电压(Vclamp)是ESD管在瞬态事件中把后端芯片"按在地板上"的唯一手段。选型时若只看工作电压和结电容,却忽略Vclamp,就等于给芯片留了一颗"定时炸弹"——ESD脉冲来临时,钳位电压高出芯片耐压仅几伏,芯片就会在纳秒级时间窗口内击穿。本文将带你一一了解ESD管选型参数核对清单、工作电压不同的ESD管有哪些?如何确定后端芯片的耐压值?以下基于实测与标准案例,说明Vclamp的选型逻辑与失效路径。

定义与测试条件

Vclamp是ESD管在额定脉冲电流(Ipp)下两端呈现的电压峰值,通常以IEC 61000-4-2 8/20μs波形为基准。例如,8kV接触放电峰值电流30A,Vclamp@30A即为芯片实际承受的电压。

动态特性

Vclamp随电流增大而升高,且与走线电感叠加形成LC振荡。某器件标称Vclamp=38V@30A,走线电感5nH时,8kV脉冲下实测峰值达58V,超过后端45V耐压而击穿。

温度漂移

Vclamp随结温升高而增大,温度系数约+0.1%/℃。85℃时Vclamp比25℃高8%,需在最高工作温度下验证。

回扫特性

部分器件具有回扫(snap-back)特性,Vclamp先升至Vtrigger,再降至Vhold,随后随电流上升。回扫可降低平均钳位电压,但Vtrigger仍需低于芯片耐压。

工艺决定上限

CMOS工艺I/O口耐压通常为工艺电压的1.2倍,3.3V工艺耐压4V,1.8V工艺耐压2.2V。GaAs射频前端耐压仅12-15V,毫米波LNA甚至<10V。

标准留余量

IEC 61000-4-2要求Vclamp ≤ 0.8×Vmax,留20%安全裕度。某Wi-Fi FEM耐压15V,Vclamp需<12V;若选用Vclamp=15V器件,8kV下动态VC=18V,直接击穿。

全温度验证

芯片耐压随温度降低,85℃时下降10%。某芯片25℃耐压5V,85℃时仅4.5V,若Vclamp=5V(常温合格),高温下即失效。

能量守恒原理

ESD脉冲能量必须在Vclamp以下完全泄放,任何超出部分都由芯片吸收。Vclamp高出1V,芯片能量吸收增加30%,失效概率指数上升。

时间窗口原理

ESD脉冲上升沿0.7ns,芯片内部ESD结构仅能承受2kV HBM,外部ESD管必须在0.5ns内将电压钳至安全值。Vclamp高出2V,芯片在0.2ns窗口内过压,击穿不可避免。

实测案例

某平板采用Vclamp=42V的ESD管,后端芯片耐压45V,8kV测试时VC动态升至48V,芯片击穿;更换为Vclamp=35V器件后,VC=38V,测试通过。

设计准则

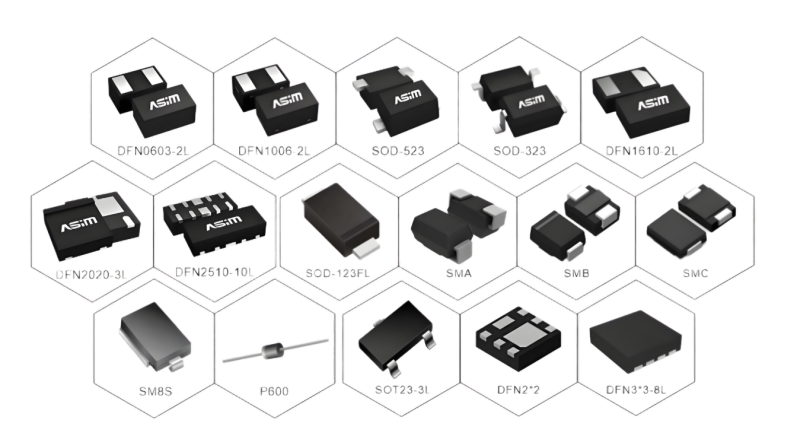

阿赛姆作为成立于2013年的综合型服务商,提供:

ESD管选型不看钳位电压,等同于让芯片在ESD事件中等死。Vclamp必须≤0.8×Vmax(全温度),并验证动态VC与走线电感影响。阿赛姆的全温度参数透明与动态测试支撑,为工程师提供了无需试错的选型保障。设计阶段必须将Vclamp作为第一优先级参数,而非事后补救。

做过EMC测试的工程师,几乎都经历过这样的场景: ESD通过了,浪涌通过了,最后死在了辐射发射上——频谱仪上一根根超标的噪声峰,宛如一把把插在心上的刀。 翻遍电路图,找不到哪里出了问题。最后发现,问题...

中国自主

品牌,更放心

多年研发经验

造就优秀产品质量

所有产品均可开具增

值专用发票

产品技术支持

7x24小时保障